# XJAnalyser

# Overview

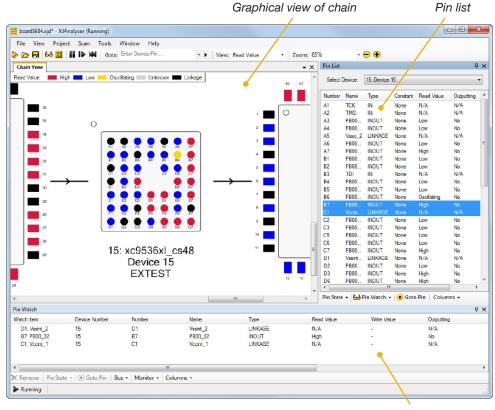

XJAnalyser is a visual analysis and debugging tool for devices in your JTAG chain. It provides instant chain verification as part of the simple setup wizard, and then gives you an interactive graphical view of the pins on your JTAG devices, including a waveform view of their logical values.

You can group pins into busses for easier control, and quickly generate toggling signals to trace connections around your board—useful when verifying shorts or opens. XJAnalyser also supports the STAPL/JAM and SVF standards for programming JTAG devices in-system.

#### Graphical circuit debugging

When tracing a net around your board with an oscilloscope, set a pin on the net to toggle and capture the signal at different points. If you slip to another pin, you will instantly know that you are no longer tracing the signal of interest.

Quickly locate signals you are sending to a device. By monitoring pins with changing values you can, for instance, press a button and quickly locate and display the pin/ball it is connected to, even if there are many thousands of pins/balls on the devices in your chain.

See the section of the chain of interest. For devices with large numbers of pins/balls, the information can become overwhelming. XJAnalyser solves this problem by enabling you to zoom in on just the balls or pins that you are interested in. You can also display multiple views of the JTAG chain, showing different areas of interest.

### Flexible control

Control the devices in your JTAG chain the way you want to. XJAnalyser offers three methods for controlling pins: directly through the graphic display, or by using the pin list or pin watch. The pin watch also allows you to group pins into busses; you can then write a value to a complete bus all at once.

#### JTAG chain interaction

The intuitive graphical interface allows rapid interaction with the devices in the JTAG chain without programming or booting any devices on your board.

Monitor the states of all the I/O pins in real-time and graphically set pins to output high, low or toggle as required.

Simplify low-level access to any devices connected to a JTAG device by grouping

### **Key Benefits**

- Allows you to increase yields by setting pin values and tracing signals you can quickly debug your boards, even under BGAs

- Speed up product development by allowing engineers to debug prototype and development boards in minutes rather than days

- Free up engineering resource by eliminating the need to write functional test software to check fundamental hardware connectivity

pins together into buses (e.g. "Data" or "Address") and setting values using convenient units (Hex, Binary, Decimal).

Avoid damaging your board — XJAnalyser generates a warning if you attempt to drive any pin to a state that would put it in conflict with a value being driven to that net from a different source.

Watch window

# XJAnalyser

## CPLD programming

You can run STAPL /JAM and SVF files within XJAnalyser. These files are typically used to program devices such as CPLDs and FPGAs. Even if these files were created for a JTAG chain containing just a single device, XJAnalyser can run them on chains containing more devices.

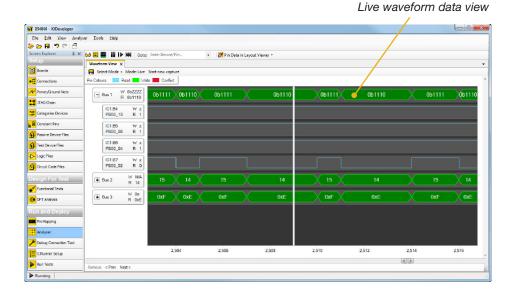

### Waveform Viewer

The Waveform Viewer captures and displays the digital signal levels and transitions of JTAG chain data.

It supports triggering, allowing circuit behaviour to be captured under specified conditions, such as when particularly events occur. This can greatly improve an engineering team's ability to capture key information and track down intermittent faults.

## Golden board comparison

You can capture the values being driven onto the JTAG devices of a known good working board. These values can then be used to identify differences between boards exhibiting unexpected behaviour and a known good board.

# Fast, simple setup

XJAnalyser has a simple setup wizard to let you start testing and debugging your board straight away. All you have to do is select a JTAG header and a library containing appropriate BSDL files and you can start working.

Even if you don't have a BSDL file, XJAnalyser will still work with the other devices.

#### Opinion Alistair Massarella CEO CRFS

**(**XJTAG is an absolute necessity for any company designing complex circuits that feature high pin count BGA or chip scale devices.**?**

**44** XJTAG is easy to use and incredibly fast, which has enabled us to shave weeks off the development schedule for our RFeye module thereby freeing our development team from time-consuming debugging tasks.<sup>1</sup>

<sup>66</sup> Test coverage is very high – we can get to over 80% of devices on the RFeye boards via the JTAG chain.<sup>33</sup>

### Features

- Able to test BGAs and fine-pitch devices

- Only BSDL files required to get the board up and running

- Set up pin states

e.g. low, high, toggling

- Trace shorts, opens and other signals

- Easy low-level access to device pins/busses

- Clear display of the pins/balls with variable zoom levels and split screen

- View JTAG chain data as waveforms

- Quickly find and monitor changing pins

- Program devices with SVF and STAPL files

- Plug and play

- Real-time interaction

# XJTAG gives you more...

XJAnalyser also includes all of the following:

- JTAG controller required to connect your PC to the circuit under test, available with a range of connectivity options

- Flexible licensing options so you can install the software on any number of PCs

- Demonstration hardware with full tutorial

- Support and upgrades for one year

Distributor / Technology Partner

Van horneplein 6 6019 BW Wessem The Netherlands Tel: +31 77 307 84 38

www.logic.nl